LPC1756FBD80Y MCU Skalierbaren Mainstream 32bit Mikrocontroller baséiert op ARM Cortex-M3 Core

♠ Produktbeschreiwung

| Produktattribut | Attributwäert |

| Hiersteller: | NXP |

| Produktkategorie: | ARM Mikrocontroller - MCU |

| RoHS: | Detailer |

| Montagestil: | SMD/SMT |

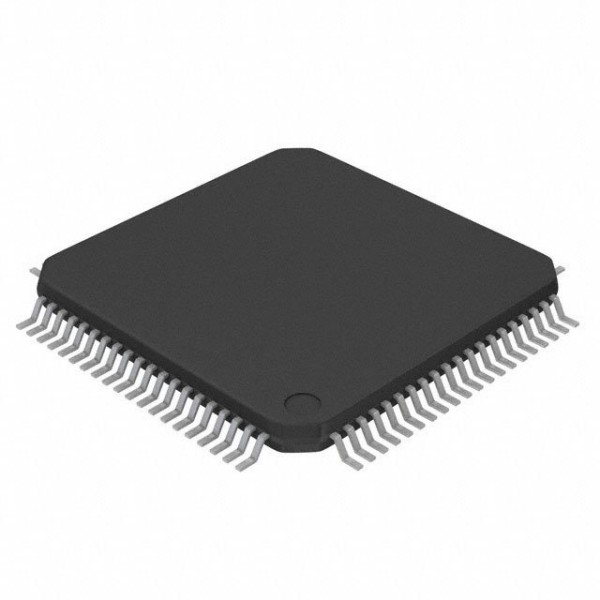

| Pak / Këscht: | LQFP-80 |

| Kär: | ARM Cortex M3 |

| Gréisst vum Programmspeicher: | 256 kB |

| Datenbusbreet: | 32-Bit |

| ADC-Opléisung: | 12-Bit |

| Maximal Taktfrequenz: | 100 MHz |

| Zuel vun den I/Oen: | 52 I/O |

| Gréisst vum Daten-RAM: | 32 kB |

| Versuergungsspannung - Min: | 2,4 V |

| Versuergungsspannung - Max: | 3,6 V |

| Minimal Betribstemperatur: | - 40°C |

| Maximal Betribstemperatur: | + 85°C |

| Verpackung: | Roll |

| Verpackung: | Band schneiden |

| Analog Versuergungsspannung: | 3,3 V |

| Mark: | NXP Semiconductors |

| DAC-Opléisung: | 10 Bit |

| Daten-RAM-Typ: | SRAM |

| Interface-Typ: | CAN, I2S, SPI, USART, USB |

| Fiichtegkeetsempfindlech: | Jo |

| Zuel vun den ADC-Kanäl: | 6 Kanäl |

| Zuel vun Timer/Zähler: | 4 Timer |

| Prozessor Serie: | LPC1756 |

| Produkt: | USB-MCU |

| Produkttyp: | ARM Mikrocontroller - MCU |

| Programmspeichertyp: | Blëtz |

| Fabréckspack Quantitéit: | 1000 |

| Ënnerkategorie: | Mikrocontroller - MCU |

| Handelsnumm: | LPC |

| Iwwerwaachungs-Timer: | Watchdog Timer, mat Fënster |

| Deel # Aliasen: | 935288606518 |

| Eenheetsgewiicht: | 0,018743 Unzen |

♠ LPC1759/58/56/54/52/51 32-Bit ARM Cortex-M3 Mikrokontroller; bis zu 512 kB Flash an 64 kB SRAM mat Ethernet, USB 2.0 Host/Apparat/OTG, CAN

D'LPC1759/58/56/54/52/51 si Mikrocontroller baséiert op ARM Cortex-M3 fir Embedded Applikatiounen, déi en héije Grad vun Integratioun a niddrege Stroumverbrauch hunn. Den ARM Cortex-M3 ass e Kär vun der nächster Generatioun, deen Systemverbesserungen ubitt, wéi verbessert Debug-Funktiounen an en héije Grad vun Ënnerstëtzungsblockintegratioun.

Den LPC1758/56/57/54/52/51 funktionéiert mat CPU-Frequenzen bis zu 100 MHz. Den LPC1759 funktionéiert mat CPU-Frequenzen bis zu 120 MHz. Den ARM Cortex-M3 CPU enthält eng 3-Stufe-Pipeline a benotzt eng Harvard-Architektur mat separaten lokalen Instruktiouns- a Datenbussen, souwéi engem drëtte Bus fir Peripheriegeräter. Den ARM Cortex-M3 CPU enthält och eng intern Prefetch-Eenheet, déi spekulativ Verzweigung ënnerstëtzt.

D'Peripherie-Ergänzung vum LPC1759/58/56/54/52/51 enthält bis zu 512 kB Flash-Speicher, bis zu 64 kB Datenspeicher, Ethernet MAC, USB Device/Host/OTG-Schnittstell, 8-Kanal-General-DMA-Controller, 4 UARTs, 2 CAN-Kanäl, 2 SSP-Controller, SPI-Schnittstell, 2 I2C-Bus-Schnittstellen, 2-Input- a 2-Output-I2S-Bus-Schnittstell, 6-Kanal-12-Bit-ADC, 10-Bit-DAC, Motorsteierung-PWM, Quadratur-Encoder-Schnittstell, 4 Allzweck-Timer, 6-Output-General-PWM, ultra-niddreg Energie-Echtzäit-Auer (RTC) mat separater Batterieversuergung, a bis zu 52 Allzweck-I/O-Pins.

eMetering

Beliichtung

Industriell Netzwierker

Alarmsystemer

Wäisswueren

Motorsteierung