P1020NXN2HFB Mikroprozessoren – MPU 800/400/667 ET NE r1.1

♠ Produktbeschreiwung

| Produktattribut | Attributwäert |

| Hiersteller: | NXP |

| Produktkategorie: | Mikroprozessoren - MPU |

| RoHS: | Detailer |

| Montagestil: | SMD/SMT |

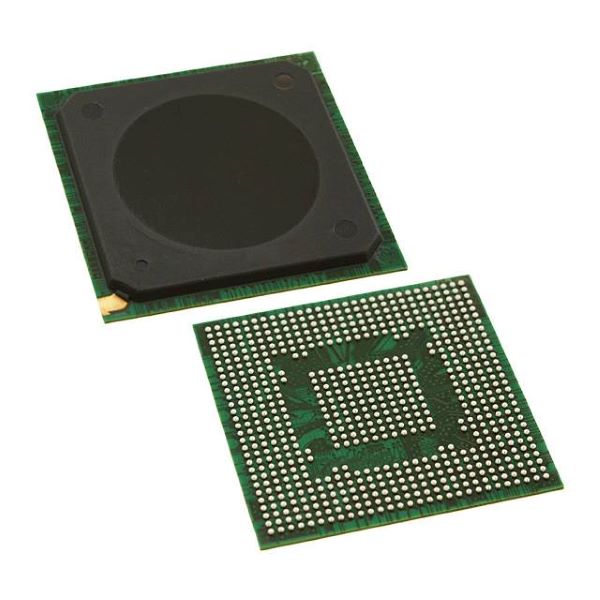

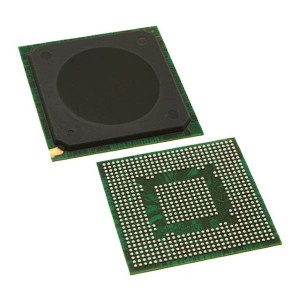

| Pak/Këscht: | TEPBGA-689 |

| Serie: | P1020 |

| Kär: | e500 |

| Zuel vun de Kären: | 2 Kär |

| Datenbusbreet: | 32-Bit |

| Maximal Taktfrequenz: | 800 MHz |

| L1 Cache Instruktiounsspeicher: | 2 x 32 kB |

| L1 Cache Datenspeicher: | 2 x 32 kB |

| Betribsspannung: | 1 V |

| Minimal Betribstemperatur: | - 40°C |

| Maximal Betribstemperatur: | + 125°C |

| Verpackung: | Schacht |

| Mark: | NXP Semiconductors |

| I/O Spannung: | 1,5 V, 1,8 V, 2,5 V, 3,3 V |

| Instruktiounsart: | Gleitkomma |

| Interface-Typ: | Ethernet, I2C, PCIe, SPI, UART, USB |

| L2 Cache-Instruktioun / Datenspeicher: | 256 kB |

| Speichertyp: | L1/L2 Cache |

| Fiichtegkeetsempfindlech: | Jo |

| Zuel vun den I/Oen: | 16 I/O |

| Prozessor Serie: | QorIQ |

| Produkttyp: | Mikroprozessoren - MPU |

| Fabréckspack Quantitéit: | 27 |

| Ënnerkategorie: | Mikroprozessoren - MPU |

| Handelsnumm: | QorIQ |

| Iwwerwaachungs-Timer: | Kee Watchdog-Timer |

| Deel # Aliasen: | 935310441557 |

| Eenheetsgewiicht: | 5,247 g |

• Duebel héichperformant 32-Bit-Kären, baséiert op der Power Architecture® Technologie:

– 36-Bit physesch Adresséierung

– Duebelpräzis Ënnerstëtzung fir Gleitkomma

– 32 Kbyte L1 Instruktiounscache an 32 Kbyte L1 Datencache fir all Kär

– Taktfrequenz vun 533 MHz bis 800 MHz

• 256 Kbyte L2 Cache mat ECC. Och konfiguréierbar als SRAM a Stashing-Speicher.

• Dräi 10/100/1000 Mbps verbessert Dräi-Geschwindegkeets-Ethernet-Controller (eTSECs)

– TCP/IP Beschleunigung, Servicequalitéit a Klassifikatiounsméiglechkeeten

– IEEE® 1588 Ënnerstëtzung

– Verloschtlos Flowkontroll

– MII, RMII, RGMII, SGMII

• Héichgeschwindegkeets-Interfaces, déi verschidde Multiplexing-Optiounen ënnerstëtzen:

– Véier SerDes bis zu 2,5 GHz/Spur, déi iwwer Controller gemultiplext ginn

– Zwee PCI Express-Schnittstellen

– Zwee SGMII-Schnittstellen

• High-Speed USB Controller (USB 2.0)

– Ënnerstëtzung fir Hosten an Apparater

– Verbessert Host Controller Interface (EHCI)

– ULPI-Schnittstell an PHY

• Verbesserten sécheren digitalen Hostcontroller (SD/MMC)

• Verbessert seriell Peripherie-Interface (eSPI)

• Integréiert Sécherheetsmotor

– Protokollënnerstëtzung ëmfaasst ARC4, 3DES, AES, RSA/ECC, RNG, Single-Pass SSL/TLS

– XOR-Beschleunigung

• 32-Bit DDR2/DDR3 SDRAM-Speichercontroller mat ECC-Ënnerstëtzung

• Programméierbaren Interrupt Controller (PIC) kompatibel mam OpenPIC Standard

• Ee véier-Kanal DMA Controller

• Zwee I2C-Controller, DUART, Timer

• Verbesserten lokalen Buscontroller (eLBC)

• TDM

• 16 allgemeng I/O Signaler

• Betribstemperatur vun der Verbindungspunkt (Tj): 0–125°C an –40°C bis 125°C (industriell Spezifikatioun)

• 31 × 31 mm 689-Pin WB-TePBGA II (Drotbindungstemperaturverstäerkt Plastik-BGA)