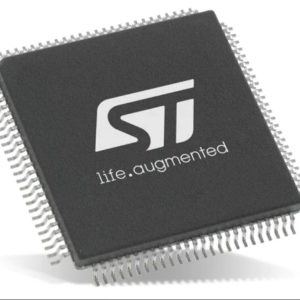

SPC563M64L5COAR 32-Bit Mikrocontroller – MCU 32-BIT Embedded MCU 80 MHz, 1,5 Mbyte

♠ Produktbeschreiwung

| Produktattribut | Attributwäert |

| Hiersteller: | STMicroelectronics |

| Produktkategorie: | 32-Bit Mikrocontroller - MCU |

| RoHS: | Detailer |

| Serie: | SPC563M64L5 |

| Montagestil: | SMD/SMT |

| Pak/Këscht: | LQFP-144 |

| Kär: | e200z335 |

| Gréisst vum Programmspeicher: | 1,5 MB |

| Gréisst vum Daten-RAM: | 94 kB |

| Datenbusbreet: | 32-Bit |

| ADC-Opléisung: | 2 x 8-Bit/10-Bit/12-Bit |

| Maximal Taktfrequenz: | 80 MHz |

| Zuel vun den I/Oen: | 105 I/O |

| Versuergungsspannung - Min: | 5 V |

| Versuergungsspannung - Max: | 5 V |

| Minimal Betribstemperatur: | - 40°C |

| Maximal Betribstemperatur: | + 125°C |

| Qualifikatioun: | AEC-Q100 |

| Verpackung: | Roll |

| Verpackung: | Band schneiden |

| Verpackung: | Mausreel |

| Mark: | STMicroelectronics |

| Fiichtegkeetsempfindlech: | Jo |

| Produkttyp: | 32-Bit Mikrocontroller - MCU |

| Fabréckspack Quantitéit: | 500 |

| Ënnerkategorie: | Mikrocontroller - MCU |

| Eenheetsgewiicht: | 1,290 g |

♠ 32-Bit Power Architecture®-baséiert MCU fir Automotive Undriffsapplikatiounen

Dës 32-Bit Automobil-Mikrocontroller sinn eng Famill vu System-on-Chip (SoC)-Geräter, déi vill nei Funktiounen zesumme mat der performanter 90-nm-CMOS-Technologie enthalen, fir eng wesentlech Reduktioun vun de Käschte pro Feature an eng bedeitend Leeschtungsverbesserung ze bidden. De fortgeschrattene a käschteeffiziente Hostprozessorkär vun dëser Automobil-Controllerfamill baséiert op der Power Architecture®-Technologie. Dës Famill enthält Verbesserungen, déi d'Architektur an Embedded-Applikatiounen verbesseren, zousätzlech Instruktiounsënnerstëtzung fir Digital Signal Processing (DSP), integréiert Technologien - wéi eng verbessert Zäitprozessoreenheet, e verbesserte Queued-Analog-Digital-Konverter, e Controller Area Network an e verbessert modulare Input-Output-System - déi fir déi haiteg Low-End-Undriffsapplikatioune wichteg sinn. Den Apparat huet en eenzegt Niveau vun der Speicherhierarchie, déi aus bis zu 94 KB On-Chip SRAM a bis zu 1,5 MB internem Flash-Speicher besteet. Den Apparat huet och eng External Bus Interface (EBI) fir 'Kalibrierung'.

■ Eenzel Ausgab, 32-Bit Power Architecture® Book E-konform e200z335 CPU-Kärkomplex

– Enthält Verbesserunge vun der Variable Length Encoding (VLE) fir d'Reduktioun vun der Codegréisst

■ 32-Kanal Direct Memory Access Controller (DMA)

■ Interrupt Controller (INTC), deen 364 Interruptquellen mat auswielbarer Prioritéit handhabe kann: 191 periphere Interruptquellen, 8 Software-Interrupts an 165 reservéiert Interrupts.

■ Frequenzmoduléiert Phasengespärte Schleif (FMPLL)

■ Kalibratioun Extern Bus-Interface (EBI)(a)

■ Systemintegratiounseenheet (SIU)

■ Bis zu 1,5 Mbyte On-Chip Flash mat Flash Controller

– Fetch Accelerator fir Single-Zyklus Flash Zougang @80 MHz

■ Bis zu 94 Kbyte statesche RAM um Chip (inklusiv bis zu 32 Kbyte Standby-RAM)

■ Boot Assist Modul (BAM)

■ 32-Kanal verbessert Zäitprozessor Eenheet vun der zweeter Generatioun (eTPU)

– 32 Standard eTPU Kanäl

– Architektonesch Verbesserunge fir d'Codeffizienz ze verbesseren an d'Flexibilitéit ze erhéijen

■ 16-Kanal verbessert modulares Input-Output System (eMIOS)

■ Verbesserten Analog-Digital-Konverter an der Warteschlang (eQADC)

■ Dezimatiounsfilter (Deel vun eQADC)

■ Temperatursensor aus Silizium

■ 2 Deserial Serial Peripheral Interface (DSPI) Moduler (kompatibel mam Mikrosekondenbus)

■ 2 verbessert Seriell Kommunikatiounsinterface (eSCI) Moduler, déi mat LIN kompatibel sinn

■ 2 Controller Area Network (FlexCAN) Moduler, déi CAN 2.0B ënnerstëtzen

■ Nexus Port Controller (NPC) no dem IEEE-ISTO 5001-2003 Standard

■ Ënnerstëtzung fir IEEE 1149.1 (JTAG)

■ Nexus-Interface

■ On-Chip Spannungsregler, deen intern 1,2 V an 3,3 V Stroum vun enger externer 5 V Quell liwwert.

■ Entworf fir LQFP144 an LQFP176