STM32H750IBK6 ARM Mikrokontroller - MCU High-Performance & DSP DP-FPU, Arm Cortex-M7 MCU 128Kbytes Flash 1MB RAM, 480

♠ Produktbeschreiwung

| Produit Attributer | Attribut Wäert |

| Hersteller: | STMicroelectronics |

| Produit Kategorie: | ARM Mikrokontroller - MCU |

| RoHS: | Detailer |

| Serie: | STM32H7 |

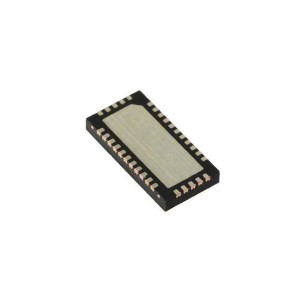

| Montage Stil: | SMD/SMT |

| Package / Fall: | UFBGA-176 |

| Kär: | ARM Cortex M7 |

| Programm Memory Gréisst: | 128 kB |

| Datebus Breet: | 32 bit |

| ADC Resolutioun: | 3 x 16 bit |

| Maximal Auer Frequenz: | 480 MHz |

| Zuel vun I/Os: | 140 I/O |

| Daten RAM Gréisst: | 1 MB |

| Versorgungsspannung - Min: | 1,62 V |

| Versuergungsspannung - Max: | 3, 6v |

| Minimum Operatioun Temperatur: | -40 C |

| Maximal Operatioun Temperatur: | +85 C |

| Verpakung: | Schacht |

| Marke: | STMicroelectronics |

| DAC Resolutioun: | 12 bit |

| Daten RAM Typ: | Ram |

| I/O Spannung: | 1,62 V bis 3,6 V |

| Interface Typ: | CAN, I2C, SAI, SDI, SPI, USART, USB |

| Feuchtigkeitempfindlech: | Jo |

| Zuel vun ADC Channels: | 36 Kanal |

| Produit: | MCU+FPU |

| Produit Typ: | ARM Mikrokontroller - MCU |

| Programm Memory Typ: | Flash |

| Factory Pack Quantitéit: | 1008 |

| Ënnerkategorie: | Mikrokontroller - MCU |

| Handelsnumm: | STM 32 |

| Watchdog Timer: | Watchdog Timer, Fënster |

| Eenheet Gewiicht: | 111 mg |

♠ 32-Bit Arm® Cortex®-M7 480MHz MCUs, 128 Kbyte Flash, 1 MB RAM, 46 com.an analog Schnëttplazen, Krypto

STM32H750xB Geräter baséieren op den High-Performance Arm® Cortex®-M7 32-Bit RISC Kär, deen op bis zu 480 MHz funktionnéiert.De Cortex® -M7 Kär huet eng Floating Point Eenheet (FPU) déi Arm® Duebelpräzis (IEEE 754 kompatibel) an eenzeg Präzisioun Datenveraarbechtungsinstruktiounen an Datentypen ënnerstëtzt.STM32H750xB Geräter ënnerstëtzen e komplette Set vun DSP Instruktiounen an eng Memory Protection Eenheet (MPU) fir d'Applikatiounssécherheet ze verbesseren.

STM32H750xB Geräter integréieren High-Speed embedded Erënnerungen mat engem Flash Memory vun 128 Kbytes, bis zu 1 Mbyte RAM (inklusiv 192 Kbytes TCM RAM, bis zu 864 Kbytes Benotzer SRAM a 4 Kbytes Backup SRAM), souwéi eng extensiv Gamme vu verstäerkte ech / Os a Peripheriegeräter verbonne mat APB Bussen, AHB Bussen, 2x32-bëssen Multi-AHB Bus Matrixentgasung an eng Multi Layer AXI interconnect Ënnerstëtzung intern an extern Erënnerung Zougang.

All d'Apparater bidden dräi ADCs, zwee DACs, zwee ultra-niddereg Kraaft Vergläicher, e Low-Power RTC, en High-Resolution Timer, 12 allgemeng Zweck 16-Bit Timer, zwee PWM Timer fir Motor Kontroll, fënnef Low-Power Timer , e richtegen Zoufallsnummergenerator (RNG), an eng kryptografesch Beschleunigungszell.D'Apparater ënnerstëtzen véier digital Filtere fir extern Sigma-Delta Modulatoren (DFSDM).Si hunn och Standard a fortgeschratt Kommunikatiounsinterfaces.

Ëmfaasst ST Staat-vun-der-Konscht patentéiert Technologie

Kär

• 32-bëssen Arm® Cortex®-M7 Kär mat duebel-Präzisioun FPU an L1 Cache: 16 Kbytes vun Donnéeën an 16 Kbytes vun Uweisunge Cache;Frequenz bis 480 MHz, MPU, 1027 DMIPS/2.14 DMIPS/MHz (Dhrystone 2.1), an DSP Instruktioune

Erënnerungen

• 128 Kbytes vun Flash Erënnerung

• 1 Mbyte RAM: 192 Kbytes TCM RAM (inkl. 64 Kbytes ITCM RAM + 128 Kbytes DTCM RAM fir Zäitkritesch Routinen), 864 Kbytes Benotzer SRAM a 4 Kbytes SRAM am Backup Domain

• Dual Modus Quad-SPI Erënnerung Interface Lafen bis zu 133 MHz

• Flexibelen externen Memory Controller mat bis zu 32-Bit Datebus: – SRAM, PSRAM, NOR Flash-Speicher op 133 MHz am Synchron-Modus geklockt – SDRAM/LPSDR SDRAM – 8/16-Bit NAND Flash-Erënnerungen

• CRC Berechnung Eenheet

Sécherheet

• ROP, PC-ROP, aktiv tamper, sécher Firmware Upgrade Ënnerstëtzung, Séchert Zougang Modus

Allgemeng Zweck Input / Ausgänge

• Bis zu 168 I / O Ports mat Ënnerbriechungsfäegkeet

Reset a Kraaftmanagement

• 3 getrennte Power-Domänen déi onofhängeg clock-gated oder ausgeschalt kënne ginn:

– D1: Héichleistungsfäegkeeten

- D2: Kommunikatioun Peripherieger an Timer

- D3: zréckgesat / Auer Kontroll / Muecht Gestioun

• 1,62 ze 3,6 V Applikatioun Fourniture an ech / Os

• POR, PDR, PVD an BOR

• Engagéierten USB-Kraaft, déi en 3.3 V internen Reguléierer embedding fir déi intern PHYs ze liwweren

• Embedded Regulator (LDO) mat konfiguréierbaren skalierbaren Ausgang fir d'digitale Circuit ze liwweren

• Spannungsskaléierung am Run an Stop Modus (6 konfiguréierbar Beräicher)

• Backupregulator (~0,9 V)

• Spannungsreferenz fir Analog Randerscheinung / VREF +

• Low-Power Modi: Schlof, Stop, Standby a VBAT ënnerstëtzen d'Batterieladung

Niddereg Stroumverbrauch

• VBAT Batterie Betribssystemer Modus mat Opluedstatiounen

• CPU an Domain Muecht Staat Iwwerwachung Pins

• 2,95 µA am Standby-Modus (Backup SRAM OFF, RTC/LSE ON)

Auer Gestioun

• VBAT Batterie Betribssystemer Modus mat Opluedstatiounen

• CPU an Domain Muecht Staat Iwwerwachung Pins

• 2,95 µA am Standby-Modus (Backup SRAM OFF, RTC/LSE ON)

Interconnect Matrix

• 3 Busmatrixen (1 AXI an 2 AHB)

• Brécke (5× AHB2-APB, 2× AXI2-AHB)

4 DMA Controller fir d'CPU ze entlaaschten

• 1× Héich-Vitesse Meeschtesch direkt Erënnerung Zougang Controller (MDMA) mat verbonne Lëscht Ënnerstëtzung

• 2 × duebel-port DMAs mat FIFO

• 1× Basis DMA mat Ufro Router Kënnen

Bis zu 35 Kommunikatioun Peripherieger

• 4 × I2Cs FM+ Interfaces (SMBus/PMBus)

• 4× USARTs/4x UARTs (ISO7816 Interface, LIN, IrDA, bis zu 12,5 Mbit/s) an 1x LPUART

• 6 × SPIs, 3 mat muxed Duplex I2S Audio Klass Genauegkeet iwwer intern Audio PLL oder extern Auer, 1x I2S am LP Domain (bis 150 MHz)

• 4x SAIs (Serial Audio Interface)

• SPDIFRX Interface

• SWPMI Single-Drot Protokoll Meeschtesch ech / F

• MDIO Sklave Interface

• 2× SD/SDIO/MMC Interfaces (bis 125 MHz)

• 2 × CAN Controller: 2 mat CAN FD, 1 mat Zäit-ausgeléist CAN (TT-CAN)

• 2 × USB OTG Interfaces (1FS, 1HS / FS) Kristalllos Léisung mat LPM a BCD

• Ethernet MAC Interface mat DMA Controller

• HDMI-CEC • 8- bis 14-Bit Kamera-Interface (bis 80 MHz)

11 Analog Peripheriegeräter

• 3 × ADCs mat 16-bëssen max.Resolutioun (bis zu 36 Kanäl, bis zu 3,6 MSPS)

• 1× Temperatur Sensor

• 2× 12-Bit D/A Konverter (1 MHz)

• 2 × ultra-niddereg-Muecht Vergläicher

• 2 × Operatiounsverstärker (7,3 MHz Bandbreedung)

• 1 × digital Filtere fir Sigma Delta Modulator (DFSDM) mat 8 Kanäl / 4 Filter

Grafiken

• LCD-TFT Controller bis zu XGA Resolutioun

• Chrom-ART grafesch Hardware Accelerator (DMA2D) fir CPU-Laascht ze reduzéieren

• Hardware JPEG Codec

Bis zu 22 Timer a Waachhënn

• 1× Héichopléisende Timer (2,1 ns maximal Opléisung)

• 2 × 32-Bit Timer mat bis zu 4 IC/OC/PWM oder Pulszähler a Quadratur (inkrementell) Encoderinput (bis 240 MHz)

• 2× 16-Bit fortgeschratt Motor Kontroll Timer (bis 240 MHz)

• 10 × 16-Bit allgemeng Zweck Timer (bis 240 MHz)

• 5 × 16-Bit Low-Power Timer (bis 240 MHz)

• 2× Waachhënn (onofhängeg a Fënster)

• 1× SysTick Timer

• RTC mat Ënner-zweet Richtegkeet an Hardware Kalenner

Kryptografesch Beschleunegung

• AES 128, 192, 256, TDES,

• HASH (MD5, SHA-1, SHA-2), HMAC

• Richteg zoufälleg Zuel Generatoren

Debug Modus

• SWD & JTAG Schnëttplazen

• 4-Kbyte Embedded Trace Buffer