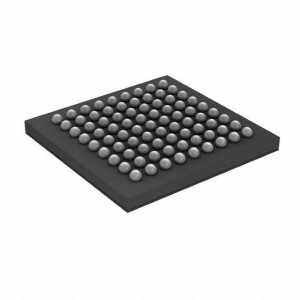

TMS320VC5509AZAY Digital Signal Prozessor & Controller - DSP, DSC Fixed-Point Digital Signal Prozessor 179-NFBGA -40 bis 85

♠ Produktbeschreiwung

| Produit Attributer | Attribut Wäert |

| Hersteller: | Texas Instrumenter |

| Produit Kategorie: | Digital Signal Prozessoren & Controller - DSP, DSC |

| RoHS: | Detailer |

| Produit: | DSPs |

| Serie: | TMS320VC5509A Ubidder |

| Montage Stil: | SMD/SMT |

| Package / Fall: | NFBGA-179 |

| Kär: | c55x |

| Zuel vu Cores: | 1 Kär |

| Maximal Auer Frequenz: | 200 MHz |

| L1 Cache Instruktioun Memory: | - |

| L1 Cache Data Memory: | - |

| Programm Memory Gréisst: | 64 kb |

| Daten RAM Gréisst: | 256 kB |

| Betribssystemer Energieversuergung Volt: | 1,6 V |

| Minimum Operatioun Temperatur: | -40 C |

| Maximal Operatioun Temperatur: | +85 C |

| Verpakung: | Schacht |

| Marke: | Texas Instrumenter |

| Uweisunge Typ: | Fixe Punkt |

| Interface Typ: | I2C |

| Feuchtigkeitempfindlech: | Jo |

| Produit Typ: | DSP - Digital Signal Prozessoren & Controller |

| Factory Pack Quantitéit: | 160 |

| Ënnerkategorie: | Embedded Prozessoren & Controller |

| Versuergungsspannung - Max: | 1,65 V |

| Versorgungsspannung - Min: | 1,55 V |

| Watchdog Timer: | Watchdog Timer |

♠ TMS320VC5509A Fixed-Point Digital Signal Prozessor

Den TMS320VC5509A Fixed Point Digital Signal Prozessor (DSP) baséiert op dem TMS320C55x DSP Generatioun CPU Prozessor Kär.D'C55x ™ DSP Architektur erreecht héich Leeschtung a geréng Kraaft duerch verstäerkte Parallelismus a total Fokus op Reduktioun vun der Kraaftdissipatioun.D'CPU ënnerstëtzt eng intern Busstruktur déi aus engem Programmbus besteet, dräi Donnéeën Liesbussen, zwee Daten Schreifbussen an zousätzlech Bussen fir Peripherie- an DMA Aktivitéit gewidmet.Dës Bussen bidden d'Fähigkeit fir bis zu dräi Donnéeën ze liesen an zwee Donnéeën ze schreiwen an engem eenzegen Zyklus.Parallel kann den DMA Controller bis zu zwee Datenübertragungen pro Zyklus onofhängeg vun der CPU Aktivitéit maachen.

D'C55x CPU bitt zwee Multiplikatiounsaccumuléiert (MAC) Eenheeten, all fäeg fir 17-Bit x 17-Bit Multiplikatioun an engem eenzegen Zyklus.Eng zentral 40-bëssen arithmetesch / logesch Eenheet (ALU) gëtt vun engem zousätzleche 16-bëssen ALU ënnerstëtzt.D'Benotzung vun den ALUs ass ënner Instruktiounsset Kontroll, déi d'Fäegkeet ubitt fir parallel Aktivitéit a Stroumverbrauch ze optimiséieren.Dës Ressourcen ginn an der Adresseenheet (AU) an der Dataunitéit (DU) vun der C55x CPU geréiert.

D'C55x DSP Generatioun ënnerstëtzt eng variabel Byte Breet Instruktiounsset fir verbessert Code Dicht.D'Instruktiounseenheet (IU) mécht 32-Bit-Programmer aus der interner oder externer Erënnerung a setzt d'Instruktioune fir d'Programmeenheet (PU).D'Programm Eenheet dekodéiert d'Instruktioune, leet Aufgaben op AU an DU Ressourcen, a geréiert déi voll geschützte Pipeline.Prädiktiv Verzweigungsfäegkeet vermeit Pipelinespülen bei der Ausféierung vun bedingte Instruktiounen.

Déi allgemeng Zwecker Input- an Outputfunktiounen an den 10-Bit A/D bidden genuch Pins fir Status, Ënnerbriechungen a Bit I/O fir LCDs, Keyboards a Medieninterfaces.Déi parallel Interface funktionnéiert an zwee Modi, entweder als Sklave fir e Mikrokontroller deen den HPI Hafen benotzt oder als Parallel Medien Interface mat der asynchroner EMIF.Serial Medien ginn duerch zwee MultiMedia Card / Secure Digital (MMC / SD) Peripherieger an dräi McBSPs ënnerstëtzt.

Den 5509A Peripherie-Set enthält en externen Memory-Interface (EMIF) deen e klénglosen Zougang zu asynchronen Erënnerungen wéi EPROM a SRAM ubitt, souwéi zu High-Speed, High-Density Erënnerungen wéi Synchron DRAM.Zousätzlech Peripherieger enthalen Universal Serial Bus (USB), Echtzäituhr, Watchdog Timer, I2C Multi-Master a Sklave Interface.Dräi Full-Duplex Multichannel gebufferten Serial Ports (McBSPs) bidden glueless Interface op eng Rei vun Industrie-Standard Serien Apparater, a Multichannel Kommunikatioun mat bis zu 128 separat aktivéiert Channels.Déi verstäerkte Host-Port-Interface (HPI) ass eng 16-Bit parallel Interface déi benotzt gëtt fir den Hostprozessor Zougang zu 32K Bytes internt Gedächtnis op der 5509A ze bidden.Den HPI kann an entweder multiplexéierten oder net-multiplexéierte Modus konfiguréiert ginn fir glueless Interface fir eng grouss Varietéit vun Hostprozessoren ze bidden.Den DMA Controller liwwert Datenbewegung fir sechs onofhängeg Kanalkontexter ouni CPU Interventioun, suergt DMA Duerchgang vu bis zu zwee 16-Bit Wierder pro Zyklus.Zwee allgemeng Zweck Timer, bis zu aacht engagéierten allgemeng Zweck I/O (GPIO) Pins, an digital Phase-locked Loop (DPLL) Clock Generatioun sinn och abegraff.

Den 5509A gëtt ënnerstëtzt vum Präis-Zouschlag eXpressDSP ™, Code Composer Studio ™ Integrated Development Environment (IDE), DSP / BIOS ™, Texas Instruments Algorithmus Standard, an de gréissten Drëtt Partei Netzwierk vun der Industrie.De Code Composer Studio IDE weist Code Generatioun Tools mat abegraff e C Compiler a Visual Linker, Simulator, RTDX ™, XDS510 ™ Emulatioun Apparat Chauffeuren, an Evaluatioun Moduler.Den 5509A gëtt och ënnerstëtzt vun der C55x DSP Bibliothéik déi méi wéi 50 Fundamental Software Kernels (FIR Filter, IIR Filter, FFTs, a verschidde Mathematikfunktiounen) souwéi Chip a Board Support Bibliothéiken huet.

Den TMS320C55x DSP Kär gouf mat enger oppener Architektur erstallt, déi d'Zousatz vun Applikatiounspezifesche Hardware erlaabt fir d'Performance op spezifesch Algorithmen ze stäerken.D'Hardwareverlängerungen op der 5509A schloen de perfekte Balance vu fixer Funktiounsleeschtung mat programméierbarer Flexibilitéit, wärend e Low-Power Konsum erreechen, a Käschten déi traditionell schwéier um Videoprozessor Maart ze fannen ass.D'Extensiounen erlaben den 5509A aussergewéinlech Videocodec-Performance mat méi wéi d'Halschent vu senger Bandbreedung ze liwweren fir zousätzlech Funktiounen auszeféieren wéi Faarfraumkonversioun, User-Interface Operatiounen, Sécherheet, TCP / IP, Stëmmerkennung an Text-zu-Speech Konversioun.Als Resultat kann een eenzegen 5509A DSP déi meescht portabel digital Videoapplikatioune mat Veraarbechtungsraum fir ze späicheren.Fir méi Informatioun, kuckt d'TMS320C55x Hardware Extensions fir Bild / Video Uwendungen Programmer Referenz (Literatur Nummer SPRU098).Fir méi Informatiounen iwwer d'Benotzung vun der DSP Image Processing Library, kuckt d'TMS320C55x Image/Video Processing Library Programmer Referenz (Literaturnummer SPRU037).

• High-Performance, Low-Power, Fixed-Point TMS320C55x™ Digital Signalprozessor

− 9.26-, 6.95-, 5-ns Instruktiounszykluszäit

- 108-, 144-, 200-MHz Auer Taux

− Een/Zwee Instruktioun(en) pro Zyklus ausgefouert

− Dual Multiplikatore [bis zu 400 Millioune Multiplikatioune akkumuléiert pro Sekonn (MMACS)]

− Zwou Arithmetesch/Logik Eenheeten (ALUs)

- Dräi intern Donnéeën / Operand Liesbussen an zwee intern Donnéeën / Operand Schreifbussen

• 128K x 16-Bit On-Chip RAM, besteet aus:

- 64K Bytes vun Dual-Access RAM (DARAM) 8 Blocks vun 4K × 16-Bit

- 192K Bytes vun Single-Access RAM (SARAM) 24 Blocks vun 4K × 16-Bit

• 64K Bytes vun One-Wait-State On-Chip ROM (32K × 16-Bit)

• 8M × 16-Bit maximal adresséierbar extern Memory Space (Synchron DRAM)

• 16-Bit Extern Parallel Bus Memory Ënnerstëtzt Entweder:

− Extern Memory Interface (EMIF) Mat GPIO Fäegkeeten a Glueless Interface fir:

- Asynchronous Static RAM (SRAM)

- Asynchron EPROM

Synchronous DRAM (SDRAM)

− 16-Bit Parallel Enhanced Host-Port Interface (EHPI) Mat GPIO Fäegkeeten

• Programmable Low-Power Kontroll vu sechs Gerät funktionell Domainen

• On-Chip Scan-baséiert Emulatioun Logik

• On-Chip Peripherieger

- Zwee 20-Bit Timer

- Watchdog Timer

- Sechs-Kanal Direct Memory Access (DMA) Controller

- Dräi Serial Ports déi eng Kombinatioun vun:

- Bis zu 3 Multichannel Buffered Serial Ports (McBSPs)

- Bis zu 2 MultiMedia / Secure Digital Card Interfaces

- Programméierbar Phase-Locked Loop Clock Generator

− Siwen (LQFP) oder Aacht (BGA) General-Purpose I/O (GPIO) Pins an en General Purpose Output Pin (XF)

− USB Full-Speed (12 Mbps) Sklaveport ënnerstëtzt Bulk, Ënnerbriechung an Isochron Transfere

- Inter-integréiert Circuit (I2C) Multi-Master a Sklaven Interface

- Echtzäituhr (RTC) Mat Kristallinput, Separat Clock Domain, Separat Stroumversuergung

− 4-Kanal (BGA) oder 2-Kanal (LQFP) 10-Bit Successiv Approximatioun A/D

• IEEE Std 1149.1† (JTAG) Grenz Scan Logik

• Packagen:

− 144-Terminal Low-Profile Quad Flatpack (LQFP) (PGE Suffix)

− 179-Terminal MicroStar BGA™ (Ball Grid Array) (GHH Suffix)

− 179-Terminal Lead-Free MicroStar BGA™ (Ball Grid Array) (ZHH Suffix)

• 1,2-V Kär (108 MHz), 2,7-V – 3,6-VI/Os

• 1,35-V Kär (144 MHz), 2,7-V – 3,6-VI/Os

• 1,6-V Kär (200 MHz), 2,7-V – 3,6-VI/Os

• Hybrid, elektresch a Kraaftzuchsystem (EV/HEV)

- Batterie Management System (BMS)

- Onboard Chargeur

- Traktioun Inverter

- DC/DC Konverter

- Starter / Generator