XC6SLX75-2FGG484C Feldprogramméierbar Gate-Array

♠ Produktbeschreiwung

| Produktattribut | Attributwäert |

| Hiersteller: | Xilinx |

| Produktkategorie: | FPGA - Feldprogramméierbar Gate-Array |

| RoHS: | Detailer |

| Serie: | XC6SLX75 |

| Zuel vun de Logikelementer: | 74637 LE |

| Zuel vun den I/Oen: | 280 I/O |

| Versuergungsspannung - Min: | 1,14 V |

| Versuergungsspannung - Max: | 1,26 V |

| Minimal Betribstemperatur: | 0 Grad Celsius |

| Maximal Betribstemperatur: | + 85°C |

| Datenrate: | - |

| Zuel vun den Transceiver: | - |

| Montagestil: | SMD/SMT |

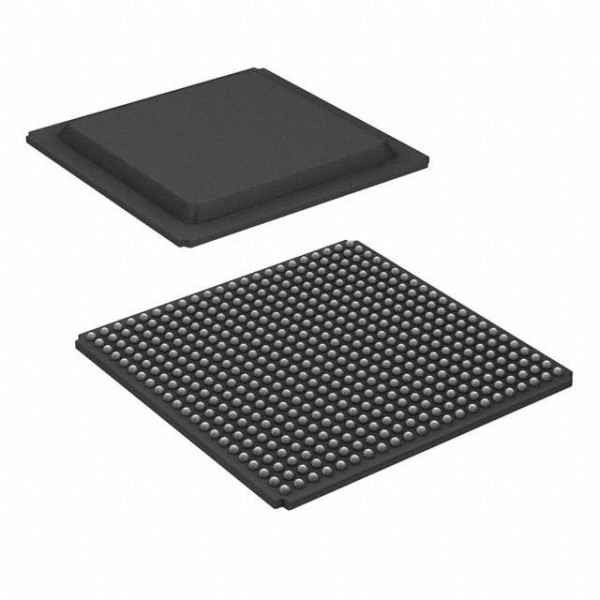

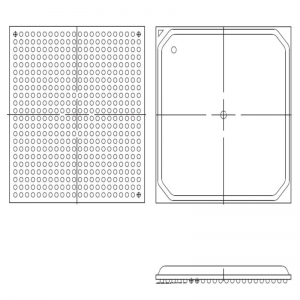

| Pak / Këscht: | FCBGA-484 |

| Mark: | Xilinx |

| Verdeelt RAM: | 692 kbit |

| Agebaute Block-RAM - EBR: | 3096 kbit |

| Maximal Betribsfrequenz: | 1080 MHz |

| Fiichtegkeetsempfindlech: | Jo |

| Zuel vun de Logik-Array-Blöcken - LABs: | 5831 LAB |

| Betribsspannung: | 1,2 V |

| Produkttyp: | FPGA - Feldprogramméierbar Gate-Array |

| Fabréckspack Quantitéit: | 1 |

| Ënnerkategorie: | Programméierbar Logik-ICs |

| Handelsnumm: | Spartanesch |

| Eenheetsgewiicht: | 1,662748 Unzen |

♠ Iwwersiicht vun der Spartan-6 Famill

D'Spartan®-6 Famill bitt féierend Systemintegratiounsméiglechkeeten mat de niddregsten Gesamtkäschte fir Uwendungen mat héije Volumen. Déi dräizéng Member Famill liwwert erweidert Dichten tëscht 3.840 an 147.443 Logikzellen, mat engem hallwe Stroumverbrauch vun de fréiere Spartan Famillen, a méi séierer, méi ëmfaassender Konnektivitéit. Gebaut op enger ausgereifter 45 nm Low-Power Kofferprozesstechnologie, déi déi optimal Balance tëscht Käschten, Leeschtung a Leeschtung liwwert, bitt d'Spartan-6 Famill eng nei, méi effizient, Dual-Register 6-Input Lookup Table (LUT) Logik an eng grouss Auswiel u agebaute Systemniveau Blöcken. Dozou gehéieren 18 Kb (2 x 9 Kb) Block RAMs, DSP48A1 Slices vun der zweeter Generatioun, SDRAM Speichercontroller, verbessert Mixed-Mode Clock Management Blöcken, SelectIO™ Technologie, energieoptimiséiert High-Speed seriell Transceiver Blöcken, PCI Express® kompatibel Endpoint Blöcken, fortgeschratt Systemniveau Stroummanagement Modi, Autodetektioun Konfiguratiounsoptiounen, a verbessert IP Sécherheet mat AES an Device DNA Schutz.

Dës Funktiounen bidden eng kostengënschteg programméierbar Alternativ zu personaliséierten ASIC-Produkter mat enger ongekënnter Benotzerfrëndlechkeet. Spartan-6 FPGAs bidden déi bescht Léisung fir Logikdesignen a grousse Volumen, konsumentorientéiert DSP-Designen a käschtesensitiv Embedded-Applikatiounen. Spartan-6 FPGAs sinn déi programméierbar Siliziumbasis fir Targeted Design Platforms, déi integréiert Software- a Hardwarekomponenten liwweren, déi et Designer erméiglechen, sech op Innovatioun ze konzentréieren, soubal hiren Entwécklungszyklus ufänkt.

• Spartan-6 Famill:

- Spartan-6 LX FPGA: Logik optimiséiert

- Spartan-6 LXT FPGA: Seriell Konnektivitéit mat héijer Geschwindegkeet

• Fir niddreg Käschten entwéckelt

- Verschidde effizient integréiert Blöcke

- Optimiséiert Auswiel vun I/O-Standarden

- Versetzte Pads

- Groussvolumen Plastik-Drotgebonnen Verpackungen

• Niddreg statesch an dynamesch Leeschtung

- 45 nm Prozess optimiséiert fir Käschten a niddreg Energieverbrauch

- Schlofmodus fir Nullstroumverbrauch

- De Suspend-Modus hält den Zoustand an d'Konfiguratioun mat Multi-Pin-Wake-up a Kontrollverbesserung ënnerhalen

- Kärspannung mat manner Leeschtung (1,0 V) (LX FPGAs, nëmmen -1 L)

- Héichleistungs-1,2V-Kärspannung (LX- an LXT-FPGAs, Geschwindegkeetsgraden -2, -3 an -3N)

• Multi-Spannungs-, Multi-Standard-SelectIO™-Interfacebanken

- Bis zu 1.080 Mb/s Dateniwwerdroungsrate pro Differential-I/O

- Auswielbaren Ausgangsantrieb, bis zu 24 mA pro Pin

- 3,3V bis 1,2VI/O Standarden a Protokoller

- Bëlleg HSTL- an SSTL-Speicherinterfaces

- Hot-Swap-Konformitéit

- Upassbar I/O-Slew-Rates fir d'Signalintegritéit ze verbesseren

• Héichgeschwindegkeets-GTP-Seriell-Transceiver an den LXT FPGAs

- Bis zu 3,2 Gb/s

- Héichgeschwindegkeets-Schnittstellen, dorënner: Serial ATA, Aurora, 1G Ethernet, PCI Express, OBSAI, CPRI, EPON, GPON, DisplayPort an XAUI

• Integréierten Endpoint-Block fir PCI Express-Designen (LXT)

• Ënnerstëtzung fir bëlleg PCI®-Technologie, kompatibel mat der 33 MHz-, 32- a 64-Bit-Spezifikatioun.

• Effizient DSP48A1-Scheiwen

- Héichleistungsarithmetik a Signalveraarbechtung

- Schnelle 18 x 18 Multiplikator an 48-Bit Akkumulator

- Pipelining- a Kaskadéierungsfäegkeet

- Pre-Adder fir Filterapplikatiounen z'ënnerstëtzen

• Integréiert Speichercontrollerblöcke

- Ënnerstëtzung fir DDR, DDR2, DDR3 an LPDDR

- Datenraten bis zu 800 Mb/s (12,8 Gb/s Spëtzebandbreet)

- Multiport-Busstruktur mat onofhängegem FIFO fir Design-Timing-Problemer ze reduzéieren

• Räichlech Logikressourcen mat erhéichter Logikkapazitéit

- Optional Ënnerstëtzung fir Schichtregister oder verdeelt RAM

- Effizient 6-Input LUTs verbesseren d'Leeschtung a miniméieren d'Energieversuergung

- LUT mat duebele Flip-Flops fir pipeline-zentresch Uwendungen

• Block RAM mat enger breeder Palette vu Granularitéit

- Schnell Block-RAM mat Byte-Schreiwaktivéierung

- 18 Kb Blocks, déi optional als zwee onofhängeg 9 Kb Block-RAMs programméiert kënne ginn

• Clock Management Tile (CMT) fir verbessert Leeschtung

- Geräuscharm, flexibel Taktfunktioun

- Digital Clock Manager (DCMs) eliminéieren Auerverzerrung a Duty Cycle Verzerrung

- Phasengespärte Schleifen (PLLs) fir Taktfreiheet mat geréngem Jitter

- Frequenzsynthese mat simultaner Multiplikatioun, Divisioun a Phasenverschiebung

- Sechzéng global Auernetzwierker mat gerénger Skewheet

• Vereinfacht Konfiguratioun, ënnerstëtzt bëlleg Standarden

- 2-Pin Autodetektiounskonfiguratioun

- Breet Ënnerstëtzung fir Drëttubidder-SPI (bis zu x4) an NOR-Flash

- Fonktiounsräiche Xilinx Plattform Flash mat JTAG

- MultiBoot-Ënnerstëtzung fir Fernupgrades mat verschiddene Bitstreams, mat Watchdog-Schutz

• Verbessert Sécherheet fir Designschutz

- Eenzegaarteg Apparat-DNA-Identifikator fir Design-Authentifikatioun

- AES Bitstream-Verschlësselung an de gréisseren Apparater

• Méi séier agebaute Veraarbechtung mat engem verbesserte, bëllegen MicroBlaze™ Softprozessor

• Industrieféierend IP- an Referenzdesignen