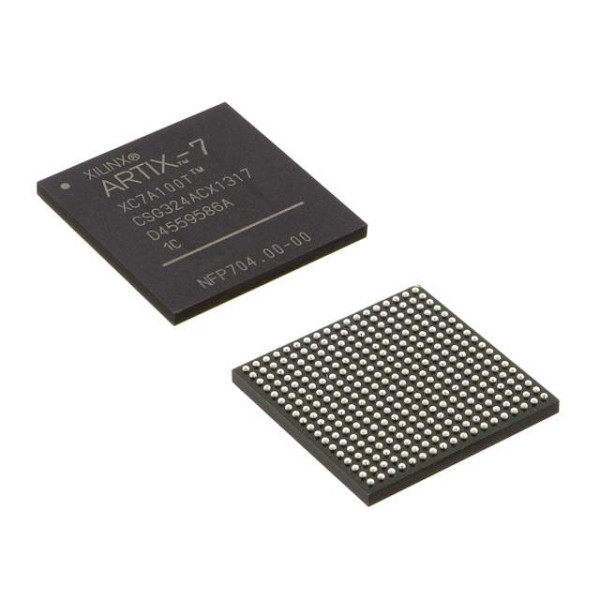

XC7A50T-2CSG324I FPGA - Feldprogramméierbar Gate Array XC7A50T-2CSG324I

♠ Produktbeschreiwung

| Produit Attributer | Attribut Wäert |

| Hersteller: | Xilinx |

| Produit Kategorie: | FPGA - Feld Programméierbar Gate Array |

| Serie: | XC7A50T Fotoen |

| Zuel vu Logik Elementer: | 52160 LE |

| Zuel vun I/Os: | 210 I/O |

| Versorgungsspannung - Min: | 0,95 V |

| Versuergungsspannung - Max: | 1,05 V |

| Minimum Operatioun Temperatur: | -40 C |

| Maximal Operatioun Temperatur: | +100 C |

| Daten Taux: | - |

| Zuel vun den Transceiver: | - |

| Montage Stil: | SMD/SMT |

| Package / Fall: | CSBGA-324 |

| Marke: | Xilinx |

| Verdeelt RAM: | 600 kbit |

| Embedded Block RAM - EBR: | 2700 kbit |

| Feuchtigkeitempfindlech: | Jo |

| Zuel vu Logic Array Blocks - LABs: | 4075 LAB |

| Betribssystemer Energieversuergung Volt: | 1 V |

| Produit Typ: | FPGA - Feld Programméierbar Gate Array |

| Factory Pack Quantitéit: | 1 |

| Ënnerkategorie: | Programméierbar Logik ICs |

| Handelsnumm: | Artix |

| Eenheet Gewiicht: | 1 oz |

♠ Xilinx® 7 Serie FPGAs enthalen véier FPGA Famillen déi de komplette Palette vu Systemfuerderunge adresséieren, rangéiert vu niddrege Käschten, klenge Formfaktor, kostenempfindlech, héichvolumen Uwendungen bis ultra High-End Konnektivitéit Bandbreedung, Logik Kapazitéit a Signalveraarbechtung Fäegkeet fir déi exigent High-Performance Uwendungen

Xilinx® 7 Serie FPGAs enthalen véier FPGA Famillen déi de komplette Palette vu Systemfuerderunge adresséieren, rangéiert vu niddrege Käschten, klenge Formfaktor, kaschtempfindlech, héichvolumen Uwendungen bis ultra High-End Konnektivitéit Bandbreedung, Logik Kapazitéit a Signalveraarbechtungsfäegkeet. fir déi exigent High-Performance Uwendungen.Déi 7 Serie FPGAs enthalen:

• Spartan®-7 Famill: Optimiséiert fir niddereg Käschten, niddregst Kraaft an héich I / O Leeschtung.Verfügbar a bëlleg, ganz kleng Formfaktor Verpackungen fir de klengste PCB Foussofdrock.

• Artix®-7 Family: Optimiséiert fir Low-Power Uwendungen déi Serien Transceiver an héich DSP a Logik Duerchgang erfuerderen.Bitt déi niddregsten Gesamtrechnung vu Materialkäschte fir héich Duerchmiesser, kaschtempfindlech Uwendungen.

• Kintex®-7 Family: Optimiséiert fir déi bescht Präisleistung mat enger 2X Verbesserung am Verglach zu der fréierer Generatioun, wat eng nei Klass vu FPGAs erméiglecht.

• Virtex®-7 Famill: Optimiséiert fir héchste Systemleistung a Kapazitéit mat enger 2X Verbesserung vun der Systemleistung.Héchste Kapazitéit Apparater aktivéiert duerch stackéiert Silicon Interconnect (SSI) Technologie.

Gebaut op enger moderner, héich performanter, niddereger Kraaft (HPL), 28 nm, High-k Metal Gate (HKMG) Prozesstechnologie, 7 Serie FPGAs erméiglechen eng oniwwertraff Erhéijung vun der Systemleistung mat 2,9 Tb/ s vun I / O bandwidth, 2 Millioune Logik Zell Kapazitéit, an 5,3 TMAC / s DSP, iwwerdeems Konsuméiere 50% manner Muecht wéi virdrun Generatioun Apparater fir eng Offer eng voll programmable Alternativ zu ASSPs an ASICs.

• Fortgeschratt héich performant FPGA Logik baséiert op real 6-Input Lookup Dësch (LUT) Technologie configurable als verdeelt Erënnerung.

• 36 Kb duebel-port Spär RAM mat gebaut-an FIFO Logik fir op-Chip Daten Puffer.

• High-Performance SelectIO™ Technologie mat Ënnerstëtzung fir DDR3 Interfaces bis zu 1.866 Mb/s.

• Héichgeschwindeg Serienverbindung mat agebaute Multi-Gigabit Transceiver vu 600 Mb / s bis max.Tariffer vun 6,6 Gb / s bis 28,05 Gb / s, bitt e spezielle Low-Power Modus, optimiséiert fir Chip-zu-Chip Interfaces.

• Eng Benotzerkonfiguréierbar Analog-Interface (XADC), déi duebel 12-Bit 1MSPS Analog-Digital-Konverter mat On-Chip thermesch a Versuergungssensoren integréiert.

• DSP Scheiwen mat 25 x 18 Multiplikator, 48-Bit Akkumulator a Pre-Adder fir High-Performance-Filterung, inklusiv optimiséiert symmetresch Koeffizientfilter.

• Mächteg Auermanagement Fliesen (CMT), kombinéiert Phase-gespaarten Loop (PLL) a Mixed-Modus Clock Manager (MMCM) Blocks fir héich Präzisioun a geréng Jitter.

• Schnell embedded Veraarbechtung mat MicroBlaze™ Prozessor ofsetzen.

• Integréiert Spär fir PCI Express® (PCIe), fir bis zu x8 Gen3 Endpoint an Root Port Designs.

• Breet Varietéit vun Configuratioun Optiounen, dorënner Ënnerstëtzung fir Commodity Erënnerungen, 256-bëssen AES Verschlësselung mat HMAC / SHA-256 Authentifikatioun, a gebaut-an SEU Detektioun a Korrektur.

• Low-Cost, Drot-Bond, Bare-Die Flip-Chip, an héich Signal Integritéit Flipchip Verpakung bitt einfach Migratioun tëscht Familljememberen am selwechte Pak.All Packagen verfügbar a Pb-gratis a ausgewielte Packagen an der Pb Optioun.

• Entworf fir héich Leeschtung an niddregsten Muecht mat 28 nm, HKMG, HPL Prozess, 1.0V Kär Volt Prozess Technologie an 0.9V Kär Volt Optioun fir nach manner Muecht.